## МИНОБРНАУКИ РОССИИ

Федеральное государственное бюджетное образовательное учреждение высшего образования

# «САРАТОВСКИЙ НАЦИОНАЛЬНЫЙ ИССЛЕДОВАТЕЛЬСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ИМЕНИ Н.Г. ЧЕРНЫШЕВСКОГО»

Кафедра физики твердого тела

## «УСТРОЙСТВА ТРОИЧНОЙ ПОСЛЕДОВАТЕЛЬНОСТНОЙ ЛОГИКИ»

## АВТОРЕФЕРАТ МАГИСТЕРСКОЙ РАБОТЫ

студента 2 курса 2251 группы направления 11.04.04 «Электроника и наноэлектроника» Института физики

## Овчинникова Константина Сергеевича

| Научный руководитель               |               |                   |

|------------------------------------|---------------|-------------------|

| профессор, д.ф м.н.                | Mariaio       | А.А. Семёнов      |

| должность, уч. степень, уч. звание | подпись, дата | инициалы, фамилия |

|                                    | 14.0          | B2029             |

| n 1 v                              |               |                   |

| Зав. кафедрой                      |               |                   |

| профессор, д.ф м.н.                | _ //          | Ал.В. Скрипаль    |

| должность, уч. степень, уч. звание | подпись, дата | инициалы, фамилия |

#### Введение

За последние двадцать лет быстродействие изготавливаемых процессоров достигло больших значений. Наблюдается приближение тактовых частот процессоров к значению в 6 ГГц. [1-3]. С 2020 года все чаще делаются предположения, что закон Мура постепенно утрачивает связь с законом масштабирования Деннарда, не характеризуя рост эффективности и производительности процессоров [4, 5]. Наблюдается тенденция к падению темпов роста быстродействия транзисторов, а вместе с ним значений тактовых частот процессоров. Однако, развитие в области программного обеспечения и алгоритмов обработки информации всё ещё имеет пространство для роста [6].

Одним из альтернативных подходов, способных обеспечить повышение производительности микропроцессорной техники, является переход цифровой техники от *двоичной* основы к *техники* системе счисления (троичной логике).

Преимуществами *троичной* системы счисления является упрощение создания и проектирования электронных схем, рост эффективности выполнения арифметических операций с помощью вычислительной техники на основе *троичной* логики.

Наряду с устройствами комбинационной логики, сигнал на выходе которых в определённый момент времени определяется комбинацией логических сигналов на входах устройств в тот же самый момент времени, существует обширный класс цифровых устройств так называемого последовательностного типа.

К устройства такого типа относятся цифровые автоматы и синхронные схемы, частным случаем которых является процессор. Основное их свойство заключается в том, что устройства последовательностного типа обеспечивают «память» цифровых систем. Базовой схемой последовательностной логики является *триггер*.

Двоичный триггер — это логическое устройство, способное хранить 1 бит данных, то есть одно из двух значений: «0» (ложь), «1» (истина).

В свою очередь троичный RS-триггер представляет собой тристабильное устройство, имеющее три устойчивых состояния и способное хранить одно из трёх логических значений: «-1» (ложь), «0» (неопределенность), «1» (истина).

Отличительной особенностью *троичного* RS-триггера от его *двоичного* аналога представляется его способность по *включению* устанавливаться в конкретное состояние: логический «0» на обоих выходах, в то время как состояние двоичного прототипа в подобной ситуации не определено.

Тем не менее, *точки* RS-триггер унаследовал от *двоичного* устройства такие неудобные, с точки зрения схемотехники синхронных цифровых систем свойства, как асинхронность и наличие «запрещенного» состояния, при котором логика его работы нарушается.

## <u> Цель научной работы</u> – исследование и разработка моделей синхронного троичного RS-триггера и D-триггера.

Исходя из поставленной выше цели, в ходе выполнения работы решались следующие задачи:

- Изучить устройство и принцип работы моделей логических элементов двоичной логики.

- Изучить устройство и принцип работы элементов двоичной последовательностной логики на примере асинхронного RS-триггера на логических вентилях «И-НЕ».

- Исследовать принципы и особенности работы синхронного двоичного RSтриггера.

- Исследовать принципы и особенности работы двоичного D-триггера.

- Исследовать принципы и особенности работы троичного RS-триггера.

- Разработать модели троичных логических элементов комбинационного типа и создать непосредственно сами работоспособные элементы

- Исследовать принципы и особенности работы троичного D-триггера.

Работа занимает 66 страниц и включает в себя 31 рисунок, список использованных источников, состоящий из 22 наименований.

## Основное содержание работы

**Во введении** рассматривается актуальность работы, определяются цель и задачи исследования. Описываются преимущества троичной логики, обосновывается выбор элементной базы.

**Первая глава** посвящена рассмотрению обзора современного состояния проблемы, на примере нескольких устройств троичной последовательностной логики. Описаны основные принципы работы, а также преимущества и недостатки устройств.

**Во второй главе** рассмотрены двоичные схемы последовательностной логики и принципы работы двоичных схем последовательностного типа. Выясняются принципы работы триггерных устройств на основе элементов резисторно-транзисторных и транзисторно-транзисторных логических семейств. Рассмотрена схемотехника бистабильных устройств на этой элементной базе [13].

Сформулированы основные свойства асинхронных RS-триггеров, фиксируются их достоинства и недостатки.

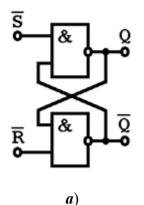

Триггером в двоичной логике принято называть логическое устройство последовательностного типа с обратными связями, обладающее двумя состояниями устойчивого равновесия (иначе говоря — бистабильная ячейка). Схема асинхронного RS—триггера на основе логических элементов «И-НЕ» представлена на рис. 1, *а*. Триггер имеет два информационных входа: Set и Reset, и два выхода: Q и /Q. Он может быть *установлен* активным уровнем логического сигнала по входу Set, при этом на выходе Q устанавливается логическая «1», или *сброшен* по входу Reset, при этом на выходе Q — логический «0». Триггер такого

типа называют асинхронным, поскольку он может быть установлен или сброшен в любой произвольный момент времени.

| № изм. | $Q_n$ | $\bar{S}$ | $\overline{R}$ | $Q_{n+1}$ |

|--------|-------|-----------|----------------|-----------|

| 1      | 1     | 1         | 1              | 1         |

| 2      | 1     | 1         | 0              | 0         |

| 3      | 0     | 1         | 1              | 0         |

| 4      | 0     | 0         | 1              | 1         |

| 5      | 1     | 1         | 1              | 1         |

| 6      | 1     | 0         | 1              | 1         |

| 7      | 1     | 1         | 1              | 1         |

| 8      | 1     | 0         | 0              | 1         |

**6**)

**Рис. 1.** Принципиальная электрическая схема асинхронного двоичного RS-триггера на элементах «И-НЕ» (a) и его таблица переходов ( $\delta$ )

Таблица RS-триггера, переходов представленная на рис. 1, **б**, иллюстрирует основные свойства этого устройства. Будучи установленным (Set) или сброшенным (Reset), триггер не реагирует в дальнейшем на состояние этого управляющего входа и сохраняет свое состояние, пока не будет переключен по входу активным Режиму другому управляющему уровнем. хранения соответствует комбинация /S = «1», /R = «1». Асинхронный RS-триггер имеет запрещенное состояние:  $/S = \langle 0 \rangle$ ,  $/R = \langle 0 \rangle$ , при котором нарушается логика его работы, заключающаяся в том, что выходы триггера (прямой – Q и инверсный – /Q) всегда находятся в противофазе

Несмотря на очевидную простоту и эффективность, данная схема имеет ряд недостатков. Во-первых, как уже было сказано выше, RS триггер является асинхронным устройством, что делает его уязвимым к состязаниям (гонкам) сигналов. Во-вторых, в нём присутствует «запрещённое» состояние, которое создаёт риск недетерминированного поведения триггера. Всё это приводит к тому, что на практике применяются обычно более сложные схемы последовательностной логики, например, синхронный RS-триггер, динамический MS-триггер [14].

**В третей главе рассмотрены** теоретические возможности создания элементов последовательностной троичной логики на основе моделей троичных

логических элементов, реализованных на базе КМОП-транзисторов [11] и биполярных транзисторов [12].

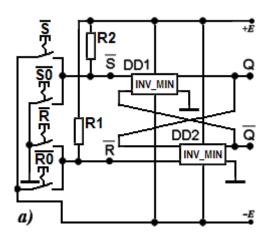

На основе двух троичных логических элементов [11,12] — аналогов двоичных вентилей «И-НЕ» — была реализована модель троичного RS-триггера, представленная на рисунке 2.

**Рис. 2.** Принципиальная электрическая схема асинхронного троичного RS-триггера на элементах «INV MIN»

В неустоявшейся окончательно терминологии троичной логики это устройство называют «триттер», чтобы отличать от его двоичного аналога. С помощью схемы, представленной на рис. 2, была измерена **таблица** логических переходов троичного RS—триттера.

Согласно представленным в таблице данным, можно сформулировать следующие свойства RS-триттера.

Активный низкий уровень напряжения (сигнал -1) на входе /S осуществляет установку троичного RS-триттера, переход в состояние Q=1, Q=-1, при условии, что на входе /R сигнал логической «1».

**Таблица** 1 Логические состояния цифровой модели троичного RS-триггера

| № | / <b>S</b> | /R | Q <sub>n-1</sub> | $/Q_{n-1}$ | Qn | /Q <sub>n</sub> | Режим              |

|---|------------|----|------------------|------------|----|-----------------|--------------------|

| 0 | 1          | 1  | -                | -          | 0  | 0               | Исходное состояние |

| 1 | 0          | 1  | 0                | 0          | 0  | 0               | Установка в 0      |

| 2 | 1          | 1  | 0                | 0          | 0  | 0               | Хранение           |

| 3 | -1         | 1  | 0                | 0          | 1  | -1              | Установка          |

| 4 | 1          | 1  | 1                | -1         | 1  | -1              | Хранение           |

| №  | / <b>S</b> | /R | Q <sub>n-1</sub> | /Q <sub>n-1</sub> | Qn | /Q <sub>n</sub> | Режим                            |

|----|------------|----|------------------|-------------------|----|-----------------|----------------------------------|

| 5  | 0          | 1  | 1                | -1                | 1  | -1              | Установка в 0                    |

| 6  | 1          | 1  | 1                | -1                | 1  | -1              | Хранение                         |

| 7  | 1          | 0  | 1                | -1                | 0  | 0               | Сброс в 0                        |

| 8  | 1          | 1  | 0                | 0                 | 0  | 0               | Хранение                         |

| 9  | 1          | -1 | 0                | 0                 | -1 | 1               | Сброс                            |

| 10 | 1          | 1  | -1               | 1                 | -1 | 1               | Хранение                         |

| 11 | 1          | 0  | -1               | 1                 | -1 | 1               | Сброс в 0                        |

| 12 | 1          | 1  | -1               | 1                 | -1 | 1               | Хранение                         |

| 13 | 0          | 1  | -1               | 1                 | 0  | 0               | Установка в 0                    |

| 14 | 1          | 1  | 0                | 0                 | 0  | 0               | Хранение                         |

| 15 | -1         | 1  | 0                | 0                 | 1  | -1              | Установка                        |

| 16 | 1          | 1  | 1                | -1                | 1  | -1              | Хранение                         |

| 17 | 0          | 1  | 1                | -1                | 1  | -1              | Установка в 0                    |

| 18 | 0          | 0  | 1                | -1                | 0  | 0               | Безусл. переход в $oldsymbol{0}$ |

| 19 | 0          | 1  | 0                | 0                 | 0  | 0               | Установка в 0                    |

| 20 | 1          | 1  | 0                | 0                 | 0  | 0               | Хранение                         |

| 21 | 1          | -1 | 0                | 0                 | -1 | 1               | Сброс                            |

| 22 | 1          | 1  | -1               | 1                 | -1 | 1               | Хранение                         |

| 23 | 1          | 0  | -1               | 1                 | -1 | 1               | Сброс в 0                        |

| 24 | 0          | 0  | -1               | 1                 | 0  | 0               | Безусл. переход в 0              |

| 25 | 0          | 1  | 0                | 0                 | 0  | 0               | Установка в 0                    |

| 26 | 1          | 1  | 0                | 0                 | 0  | 0               | Хранение                         |

| 27 | -1         | 1  | 0                | 0                 | 1  | -1              | Установка                        |

| 28 | 1          | 1  | 1                | -1                | 1  | -1              | Хранение                         |

| 29 | 0          | 1  | 1                | -1                | 1  | -1              | Установка в 0                    |

| 30 | 0          | -1 | 1                | -1                | 0  | 1               | Неуст. состояние                 |

| 31 | 0          | 1  | 0                | 1                 | 0  | 0               | Установка в <b>0</b>             |

| 32 | 1          | 1  | 0                | 0                 | 0  | 0               | Хранение                         |

| 33 | 1          | -1 | 0                | 0                 | -1 | 1               | Сброс                            |

| 34 | 1          | 1  | -1               | 1                 | -1 | 1               | Хранение                         |

| 35 | 1          | 0  | -1               | 1                 | -1 | 1               | Сброс в 0                        |

| 36 | -1         | 0  | -1               | 1                 | 1  | 0               | Неуст. состояние                 |

| 37 | 1          | 0  | 1                | 0                 | 0  | 0               | Сброс в 0                        |

| 38 | 1          | 1  | 0                | 0                 | 0  | 0               | Хранение                         |

| 39 | -1         | -1 | 0                | 0                 | 1  | 1               | Неуст. состояние                 |

| 40 | 1          | 1  | 1                | 1                 | 1  | -1              | Хранение                         |

Активный низкий уровень напряжения (сигнал -1) на входе /R, осуществляет сброс троичного RS-триттера, переход в состояние Q = -1, Q = 1, при условии, что на входе /S сигнал логической «1».

Будучи установленным или сброшенным, RS-триттер не реагирует в

дальнейшем на сигналы соответствующего управляющего входа и сохраняет свое состояние, пока не будет переключен по другому управляющему входу активным уровнем. Так же, как и двоичный прототип, RS-триттер хранит своё состояние при /S=1, /R=1.

Очевидно, что эти свойства характерны и для двоичного прототипа асинхронного RS-триттера. Но RS-триттер имеет и свои уникальные свойства, обусловленные логикой работы троичных вентилей «И-НЕ».

При включении RS-триттер устанавливается обычно в состояние «не определено»  $Q=0,\,/Q=0.$

Будучи установленным, RS-триттер может быть сброшен в состояние неопределенности Q=0, Q=0 только по входу /R логическим уровнем «0».

Будучи сброшенным, RS-триттер может быть установлен в состояние «не определено» Q=0, /Q=0 только по входу /S логическим уровнем «0».

Асинхронный RS-триттер имеет несколько запрещенных состояний при /S = -1, /R = -1; /S = -1, /R = 0; /S = 0, /R = -1; поскольку при этом нарушается логика его работы, предполагающая, что выходы Q и /Q всегда находятся в противофазе. Такие состояния неустойчивы.

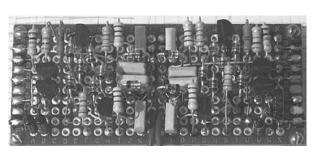

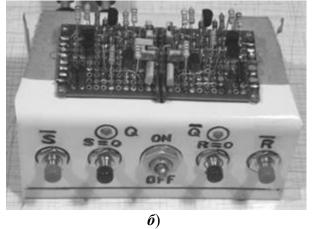

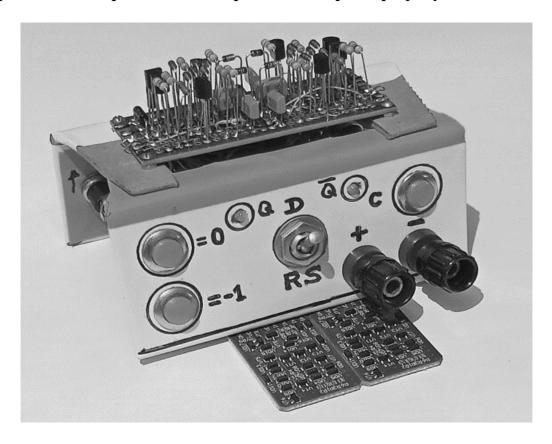

Для экспериментальной проверки работы RS-триттера на отечественной элементной базе — биполярных транзисторах типов KT3102, KT3107, KT315, KT361 [15] — был выполнен рабочий макет двух элементов ТТЛ троичной логики — аналогов двоичных вентилей «И-НЕ» по схеме, представленной в [12]. Внешний вид макета представлен на рис. 3, *a*.

Для измерения экспериментальной таблицы логических переходов макета троичного RS-триггера был изготовлен стенд, внешний вид которого представлен на рис. 3,  $\boldsymbol{\delta}$  [16].

a)

**Рис. 3.** Макет двух троичных логических элементов «INV-MIN» ТТЛ (a) и макет RS-триттера на основе логических элементов «INV-MIN» ТТЛ ( $\delta$ )

Экспериментальные результаты полностью подтвердили данные, полученные при анализе теоретической модели троичного RS-триггера в программном пакете САПР, и приведённые ранее в таблице.

В четвертой главе исследуется троичный D-триггер Троичный D-триггер - это устройство, которое используется для хранения и обработки информации в троичной логике. Он имеет три состояния: 0, 1 и Z (или "don't care").

Принцип работы троичного D-триггера заключается в том, что если на входе D присутствует сигнал (D = 1), то триггер переключается в состояние 1. Если на входе D отсутствует сигнал (D = 0), то триггер остается в текущем состоянии. Если на вход C подается сигнал (C = 1), то происходит сброс триггера в нулевое состояние.

Преимущества троичного D-триггера заключаются в том, что он хранит информацию. Это означает, что он способен сохранять три разных значения (состояния) для каждого бита информации, в отличие от обычного двоичного D-триггера, который может хранить только два состояния (0 и 1).

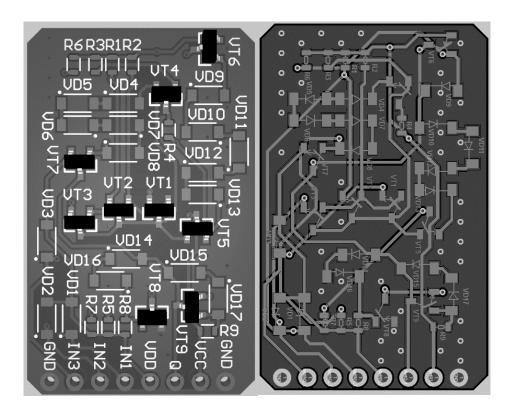

Представлен макет троичного D-триттера а также была разработана печатная плата в виде модуля на миниатюрных элементах для проверки монтажа.

Рисунок 4. Плата «И-НЕ» (INV-MIN) троичной логики

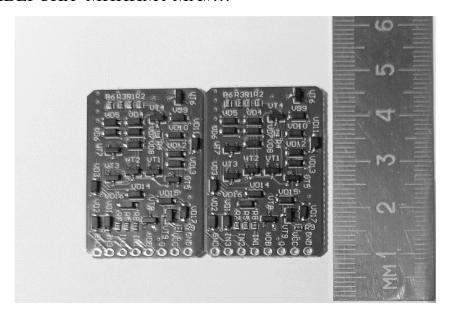

Были также изготовлены сами модули троичных логических элементов «ИНВЕРСИЯ МИНИМУМА»...

Рисунок 5. Модули «И-НЕ» (INV-MIN) троичной логики

На основе которых был модифицирован макет **троичного асинхронного RS-триггера** для измерения экспериментальной таблицы логических переходов разработанного **троичного синхронного D-триггера** рисунок 6.

## Рисунок 6. Макет синхронного D-триттера

Индикация состояний выходов **D-триТТера** обеспечивается двухцветными светодиодами: состоянию логической «1» соответствует красный цвет свечения, «—1» — зелёный цвет свечения, в состоянии «0» светодиоды не светятся.

Таблица 2- Логические состояния троичного D-триттера

| №  | D  | C  | / <b>S</b> | /R | Q <sub>n-1</sub> | $/\mathbf{Q}_{n-1}$ | Qn | /Qn | Режим          |

|----|----|----|------------|----|------------------|---------------------|----|-----|----------------|

| 0  | 1  | -1 | 1          | 1  | -                | -                   | 0  | 0   | Исх. состояние |

| 1  | 0  | -1 | 1          | 1  | 0                | 0                   | 0  | 0   | Хранение       |

| 2  | 1  | -1 | 1          | 1  | 0                | 0                   | 0  | 0   | Хранение       |

| 3  | -1 | -1 | 1          | 1  | 0                | 0                   | 0  | 0   | Хранение       |

| 4  | 1  | -1 | 1          | 1  | 0                | 0                   | 0  | 0   | Хранение       |

| 5  | 1  | 1  | -1         | 1  | 0                | 0                   | 1  | -1  | Запись 1       |

| 6  | 1  | -1 | 1          | 1  | 1                | -1                  | 1  | -1  | Хранение       |

| 7  | 0  | -1 | 1          | 1  | 1                | -1                  | 1  | -1  | Хранение       |

| 8  | 1  | -1 | 1          | 1  | 1                | -1                  | 1  | -1  | Хранение       |

| 9  | -1 | -1 | 1          | 1  | 1                | -1                  | 1  | -1  | Хранение       |

| 10 | -1 | 1  | 1          | -1 | 1                | -1                  | -1 | 1   | Запись -1      |

| 11 | -1 | -1 | 1          | 1  | -1               | 1                   | -1 | 1   | Хранение       |

| 12 | 1  | -1 | 1          | 1  | -1               | 1                   | -1 | 1   | Хранение       |

| 13 | 0  | -1 | 1          | 1  | -1               | 1                   | -1 | 1   | Хранение       |

| 14 | 0  | 1  | 0          | 0  | -1               | 1                   | 0  | 0   | Запись 0       |

| 15 | 0  | -1 | 1          | 1  | 0                | 0                   | 0  | 0   | Хранение       |

| 16 | 1  | -1 | 1          | 1  | 0                | 0                   | 0  | 0   | Хранение       |

Таблица полностью подтверждает результаты, полученные при анализе теоретической модели **синхронного D-триТТера** в программном пакете САПР.

#### Заключение.

В ходе выполнения данной квалификационной работы магистра были достигнуты следующие результаты:

Выполнены цифровые модели разработанных устройств в программном пакете САПР, а также их действующие макеты на типовых дискретных электронных компонентах.

Теоретически и экспериментально исследовано функционирование синхронных троичных триггеров со статическим управлением, выявлены базовые принципы их работы и характерные особенности.

Во избежание нештатной работы синхронных троичных триггеров со статическим управлением сигнал на тактовом входе С должен иметь небольшую длительность, а также крутые фронты. Для этого рекомендуется осуществлять управление синхронными троичными триггерами выходом двоичного логического элемента или троичного декодера.

Были разработаны модули «И-НЕ» (INV-MIN) троичной логики, а так же действующий макет синхронного D-триттера.

Экспериментально подтвердили результаты, полученные при анализе теоретической модели **синхронного D-триТТера** в программном пакете САПР.

Разработанные схемотехнические решения могут быть использованы для создания динамических троичных триггеров типа «ведущий-ведомый», а также счётных троичных триггеров.

## Список использованных источников

- 1. Брусенцов Н.П., Маслов С.П., Розин В.П., Тишулина А.М. Малая цифровая вычислительная машина "Сетунь", Изд-во МГУ, М., 1965.

- 2. Брусенцов Н.П. Заметки о троичной цифровой технике (6-е продолжение). // Архитектура и программное оснащение цифровых систем. М.: Изд-во Моск. ун-та, 1984. С.114-123.

- 3. Диалоговая система структурированного программирования ДССП. // Брусенцов Н.П. Микрокомпьютеры. М.: "Наука", 1985. С.141-170.

- 4. Диалоговая система структурированного программирования ДССП-80. / Н.П.Брусенцов, В.Б.Захаров, И.А.Руднев, С.А.Сидоров. // Диалоговые микрокомпьютерные системы. - М.: Изд-во Моск. ун-та, 1986. С.3-27.

- 5. Интегрированная система обучения, конструирования программ и разработки дидактических материалов (Учебно-методическое пособие)/ Под ред. Н.П. Брусенцова. М.: Изд-во ф-та ВМиК МГУ, 1996. 13. Опыт создания троичных цифровых машин. / Н.П.Брусенцов, Е.А.Жоголев, С.П.Маслов, Х.Рамиль Альварес. // Компьютеры в Европе, Прошлое, настоящее и будущее. Киев, "Феникс", 1998. С.67-71.

- 6. Брусенцов Н.П., Захаров В.Б., Руднев С.А., Сидоров С.А., Чанышев Н.А. Развиваемый адаптивный язык РАЯ диалоговой системы программирования ДССП. М.: Изд-во Моск. Ун-та, 1987 г. 80 с.

- 7. Frieder G., Luk C. Algorithms for binary coded balanced and ordinary ternary operations // IEEE Trans. Comput. 1975. V. 24. P. 212--215.

- 8. R. Mariani, R. Roncella, R. Saletti, P. Terreni. "On the Realisation of Delay-Insensitive Asynchronous Circuits with CMOS Ternary Logic", Third International Symposium on Advanced Research in Asynchronous Circuits and Systems (ASYNC '97), p. 54, 1997.

- 9. Семёнов А.А. Модели троичных элементов и их применение в схемотехнике процессоров // А.А. Семёнов, А.С. Дронкин Взаимодействие сверхвысокочастотного, терагерцового и оптического излучения с полупроводниковыми микро- и наноструктурами, метаматериалами и биообъектами: Сборник статей восьмой Всероссийской научной школысеминара / под ред. проф. Ал.В. Скрипаля Саратов: Изд-во «Саратовский источник», 2021. 280 с.:ил.

- 10. Семёнов А.А. Базовые элементы троичной транзисторно-транзисторной логики // А.А. Семёнов, А.С. Дронкин Взаимодействие сверхвысокочастотного, терагерцового и оптического излучения с полупроводниковыми микро- и наноструктурами, метаматериалами и биообъектами: Сборник статей девятой Всероссийской научной школысеминара / под ред. проф. Ал.В. Скрипаля Саратов: Изд-во «Саратовский источник», 2022. С. 52-56.

- 11. Хоровиц П., Хилл У. Искусство схемотехники. Т.1. Перевод с англ. под ред. М.В. Гальперина. М.: Мир, <math>1983, с. 540.

- 12.Шило В.Л. Популярные цифровые микросхемы: Справочник. // В.Л. Шило 2-е изд., исправленное. М.: Радио и связь, 1989. 352 с.:ил.

- 13.Прокопенко Н.Н., Чернов Н.И., Югай В.Я. Линейный логический синтез двузначных цифровых структур в линейных пространствах // Труды конгресса по интеллектуальным системам и информационным технологиям IS&IT'13. М.: Физматлит, 2013. С. 278-283

- 14.Касперски К. Техника оптимизации программ. // Эффективное использование памяти. -П.: БХВ, 2003г. 560с.

- 15. Чернов Н.И., Югай В.Я. Неклассический синтез цифровых структур средствами аналоговой схемотехники // Проблемы современной аналоговой схемотехники: Сб. материалов IX Международного научно-практического семинара / Под ред. Н.Н. Прокопенко. Шахты: Изд-во ФГБОУ ВПО «ЮРГУЭС», 2012. С. 138-143.

- 16. С.В. Якубовский, Л.И. Ниссельсон, <u>Кулешова В.И.</u> Цифровые и аналоговые интегральные микросхемы: Справочник // Под редакцией С.В. Якубовский М.: Радио и связь, 1990. 496 с.

- 17. Транзисторы для аппаратуры широкого применения: Справочник / К.М. Брежнева, Е.И. Гантман, Т.И. Давыдова и др. Под ред. Б.Л.Перельмана. М.: Радио и связь, 1981, 656 с.

- 18. Алексенко А.Г., Галицын А.А., Иванников А.Д. Проектирование радиоэлектронной аппаратуры на микропроцессорах // Программирование, типовые решения, методы отладки. М.: Радио и связь, 1999г. 420с.

- 19. Овчинников К.С. Элементы троичной последовательностной логики // К.С. Овчинников, А.С. Дронкин, А.А. Семёнов Взаимодействие сверхвысокочастотного, терагерцового и оптического излучения с полупроводнико2выми микро- и наноструктурами, метаматериалами и биообъектами: Сборник статей девятой Всероссийской научной школысеминара / под ред. проф. Ал.В. Скрипаля Саратов: Изд-во «Саратовский источник», 2022. С. 57-61.

- 20. Белюченко И. М. Особенности помехозащиты троичного кода // Электротехнические и информационные комплексы и системы. 2009. Т. 5. № 4. С. 17–22.

- 21. Кулакова А.А., Лукьяненко Е.Б. Энергоэффективные КМОП-триггеры с инверторной запоминающей ячейкой // Изв. вузов. Электроника. 2019.  $T.\ 24.\ -NO$  3.  $C.\ 230$ —238. DOI: 10.24151/1561-5405-2019-24-3-230-238

- **22.** Сапожников Вал. В. Синтез синхронных автоматов по заданной временной входной выходной последовательности / Вал. В. Сапожников, Вл. В. Сапожников, Д. В. Ефанов. Санкт-Петебруг: ПГУПС, 2010. 28 с